最新曝光的酷睿Ultra 200S内核细节显示,台积电几乎全面参与制造,据悉,Intel仅提供22nm基板,而该内核的具体性能和技术细节尚未公布,这一消息引发了业界对于未来酷睿处理器性能和制造模式的关注与讨论。

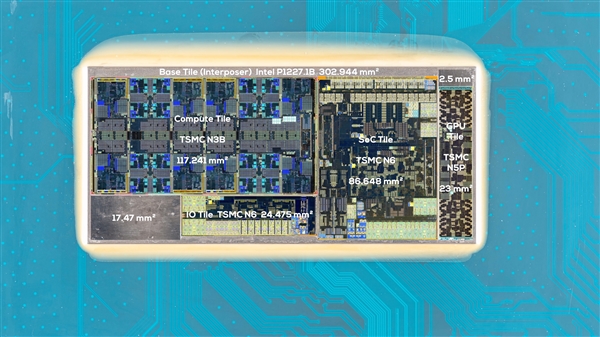

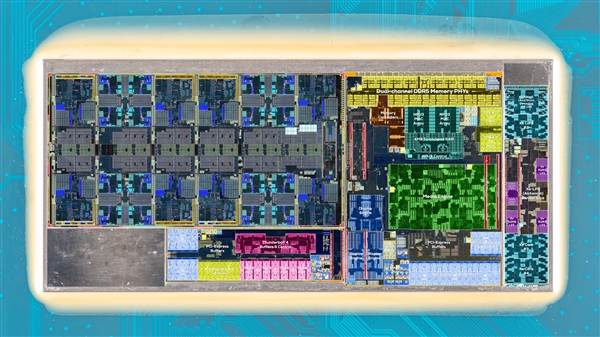

电脑知识网5月6日报道,备受瞩目的酷睿Ultra 200S系列已经发布一段时间了,我们终于看到了其内核布局的详尽细节,包括不同模块的布局、具体的制造工艺和面积,该系列的代号Arrow Lake采用了创新的chiplet芯粒设计,分为四个不同的模块,均由台积电制造,值得一提的是,这是首个几乎完全采用外部代工的产品。

Compute Tile计算模块:采用台积电先进的N3B 3nm工艺,面积达到117.241平方毫米。

GPU Tile核显模块:采用台积电N5P 5nm工艺,面积为23平方毫米。

SoC Tile系统单元模块:采用台积电N6 6nm工艺,面积为86.648平方毫米,这个模块相对复杂,包括第三代NPU引擎、DDR5内存控制器、媒体引擎、显示引擎等。

IO Tile输入输出模块:同样采用台积电N6 6nm工艺,面积为24.475平方毫米,它主要服务于雷电4和更多的PCIe,包括两组PCIe 5.0 x4物理层以及缓冲,PCIe 4.0 x8物理层,雷电4物理层、缓冲、显示物理层等。

还有两个用于补充和支撑整体结构的填充模块,面积分别为2.5平方毫米和17.47平方毫米。

在所有模块之下,是基板(中介层),这是Intel的16工艺制造的部分,它并非全新的发明,而是在原有的22FFL 22nm工艺基础上升级而来(型号为P1227.1B),面积为302.994平方毫米。

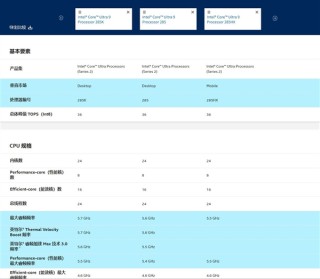

以下是内核布局的具体细节:可以看到八个性能核(P核)和16个效率核(E核),E核分为四个集群,与P核交错分布在一个名为Ring Agent的环形总线上,二级缓存方面,每个P核有3MB,每组四个E核共享4MB,并分为三个部分,三级缓存则是每个P核和每组E核各有3MB。

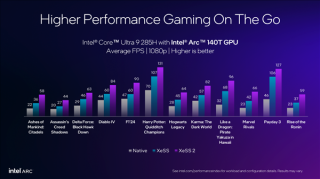

核显模块与Meteor Lake上的设计相似,仍然采用Alchemist架构的Xe-LPG核心,每个核心内部配备了八组Dual-XVE计算引擎,并配备不同规模的一二级缓存。

酷睿Ultra 200S系列的内核设计是一项复杂的工程,展示了Intel与台积电的紧密合作以及先进的芯片制造技术,随着更多细节的曝光,我们期待这一系列产品在市场上的表现。