前不久,三大国际EDA公司已经接到美国商务部BIS通知,要求暂停对整个中国大陆地区的涉及EDA和IP产品服务与支持。这意味着针对中国半导体行业的限制禁令已经达到了极端约束,中国先进芯片技术将完全依赖于中国EDA供应链自主可控。

日前,合见工软作为中国数字EDA/IP龙头企业在上海召开了“2025合见工软新产品发布会暨技术研讨会”,会上展示了下一代国产EDA技术的重大革新进展,并正式发布了多款国产自主自研EDA及IP产品,助力我国自研EDA和IP产品从国产化替代到国际标杆技术的进阶。

从断供后的开放免费试用,到快速发布多款可比肩国际标杆水平的EDA工具,合见工软以一套组合拳快速应对了国际EDA禁售的挑战,重塑了中国EDA自主可控的新态势。

本次合见工软正式发布的五款创新产品包括:

数字验证下一代硬件产品:下一代全场景验证硬件系统UniVista Unified Verification Hardware System Gen2(UVHS-2)国产数字仿真调试EDA重大进展:下一代全功能高性能数字仿真器UniVista Simulator Plus (UVS+)下一代全功能高效能数字验证调试平台UniVista Debugger Plus (UVD+)全国产自主知识产权高速接口IP解决方案:推动智算互联的超以太网IP解决方案UniVista UEC MAC IP 先进工艺多协议兼容、集成化传输接口SerDes IP解决方案

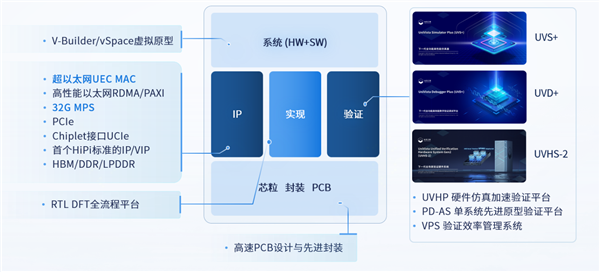

合见工软现有产品已覆盖数字芯片EDA工具、系统级工具及高端IP,是国内唯一一家可以完整覆盖数字芯片验证全流程,DFT可测性设计全流程,并同时提供先进工艺高速互联IP的国产EDA公司。自成立以来,合见工软一直以国际先进水平为目标,多产品线并行研发,为中国半导体企业提供了芯片硅前和硅后的高性能EDA工具和IP解决方案。

此次发布的下一代EDA战略,合见工软将数字验证最核心的基础工具——数字仿真/调试器,及支持大规模芯片设计的高端硬件验证平台,均实现了架构级迭代创新,是国产EDA技术创新的重大进展,多项性能比肩国际标杆水平,目标是打破数字高端大芯片验证EDA的国际厂商垄断。

同时,合见工软已在国内自研IP领域取得了快速的技术进展和客户增长,在国内自主自研高速接口IP的市场份额中已居前列。目前,合见工软的高速接口IP解决方案已实现了国产化技术突破,支持国内外先进工艺,并得到多家商业客户的成功流片和数百家客户的商业部署。合见工软的智算芯片互联IP解决方案,覆盖国内外先进标准,助力智算、HPC、通信、自动驾驶、工业物联网等领域大算力芯片的性能突破及爆发式发展。特别在当前国际先进EDA工具和制程受限的情况下,合见工软对高端芯片设计企业的产品与技术支持,助力了中国超算和AI类芯片企业打造自主可控的上下游供应链。

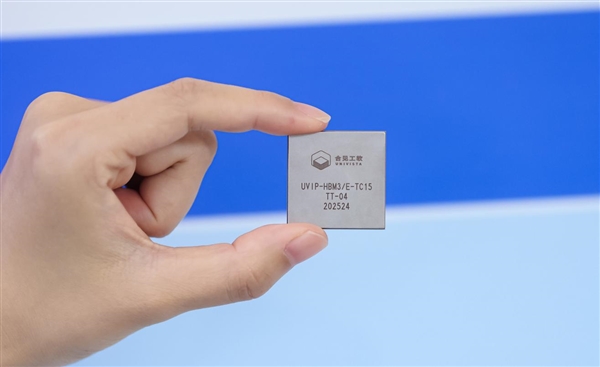

特别值得一提的是,在此次发布会上,合见工软宣布已经成功点亮HBM3/E测试芯片,基于标准电压实现高达9600MT/s的数据传输。合见工软提供高性能自研 HBM3/E IP控制器和PHY整体解决方案,控制器支持超低的读写延迟可以根据客户读写Pattern做定制化设计,加强的抗衰减和Deskew能力可以应对各种复杂场景设计,内置处理器可以灵活支持多种Training算法,完整的2.5D interposer和SIPI分析服务可以帮助客户通过端到端优化提升HBM3/E系统运行速度。自研HBM3/E控制器和PHY,广泛支持业界的各种颗粒,帮助客户在实际的系统中真正实现高性能。

先进工艺HBM3/E测试芯片

在地缘政治和技术壁垒不断加剧的时代,中国半导体企业面临着芯片设计与系统设计工具的重重技术封锁与挑战,考验着国产EDA企业的真正技术水平与发展韧性。只有真正经过用户打磨验证的EDA工具,才能建立可持续的商业生态,与国际垄断企业开启真正的技术竞赛。特别是此次美国EDA断供的全面危机之时,合见工软在此前正式向用户免费开放关键产品试用与评估服务。在当前国产工具普遍“缺乏市场验证”的挑战下,证明了合见工软产品在规模化应用和强大技术支持方面的能力,只有真正经过用户打磨验证的工具才能具备持久的竞争力。

EDA与IP是中国科技自主化进程中的关键一战,合见工软以四年近40款产品的创新速度、硬核的技术实力,赢得了客户的信任与国内集成电路行业的广泛认可,同时引领了中国EDA企业发展与生态建设的新态势。

合见工软产品布局

数字验证核心工具重大革新:全功能数字仿真调试平台UVS+/UVD+

合见工软今日宣布,数字芯片验证的核心仿真调试工具已取得重大进展,正式发布国产自研下一代全功能高性能数字仿真器UniVista Simulator Plus (UVS+)和下一代全功能高效能数字验证调试平台UniVista Debugger Plus (UVD+)。新一代仿真器UVS+打造全国产一站式验证流程,全自研架构,并支持国产服务器生态,可比肩国际领先厂商的仿真、编译及波形处理的先进性能,大幅加速验证流程;全面覆盖支持现代芯片验证所需的数字仿真功能和各项特殊应用场景需求。新一代调试平台UVD+集成更多高阶功能,提供全场景调试能力,创新的数据处理架构提升验证调试效率,并打造全新视觉观感,多维提升调试体验。

2021年10月,合见工软推出了国内首款自主自研的商用级数字仿真器,正式打破了国际EDA高端仿真工具的垄断,对EDA国产化意义重大。三年多以来,UVS系列已经过百万量级客户实战项目用例打磨淬炼和持续迭代优化,已在50多个关键芯片项目中成功应用,得到了国内头部客户的认可,积累了丰富的行业经验。

合见工软现可提供高性能自主可控的国产数字验证EDA全流程工具,此次发布的数字仿真器UVS+和数字验证调试平台UVD+是合见工软数字EDA验证全流程的核心基础工具,结合最新发布的下一代全场景验证硬件系统UVHS-2,以及数据中心级全场景超大容量硬件仿真加速验证平台UVHP,单系统先进原型验证平台PD-AS,虚拟原型设计与仿真工具套件V-Builder/vSpace,验证管理软件VPS等产品组合,全面覆盖从早期虚拟架构设计建模、中期硬件仿真加速、中期子系统级软件到后期全芯片级原型验证的全场景需求。

合见工软国产数字验证EDA全流程工具

合见工软联席总裁郭立阜表示:“国产EDA工具链的自主可控对于打造安全、高效、可持续的芯片产业环境至关重要。而芯片设计验证占据总设计周期的70%以上,直接影响产品上市时间和质量,只有高性能与可靠性并重的验证工具,才是保障客户项目成功的关键。合见工软数字仿真及调试工具经过与国内头部芯片设计企业紧密合作,历经三年淬炼迭代,第二代UVS+与UVD+工具平台带来性能上的飞跃。全自研架构自主可控带来可靠性的全面提升,提升供应链韧性,为中国芯片设计项目保驾护航,抵御外部风险,为‘中国芯’的创新提供沃土。”

客户评价:

中兴微电子有线系统部部长贺志强表示:“作为合见工软的深度战略合作伙伴,我们在2021年自第一代UVS/UVD诞生时起,就将其应用于项目的验证流程。四年来,我们与合见工软的研发技术团队共同见证了这款国产EDA工具经过无数次打磨迭代后的全面系统性升级。并很高兴地看到第二代UVS+/UVD+所取得的诸多技术进展和架构革新。

UVS+在复杂SoC场景的对比测试中展现出与国际领先水平相当的稳定性和性能,在近期芯片回归测试中体现了扎实的软件产品化成熟度;同时,UVD+打造了创新的GUI设计,其直观的调试工作流和智能诊断能力为调试工作提供了更高效的设计洞察,显著提升了问题根因定位的精准度和效率。

这些进步标志着国产验证工具正加速从‘可用’向‘好用’的技术拐点迈进。面对当前高复杂度芯片设计的挑战,我们期待合见工软持续深耕本土化场景创新,在保持技术演进势头的同时,进一步强化对中国芯片设计流程的深度适配,为产业构建自主可控、高效协同的工具链新生态。”

更多信息,请访问:

下一代全功能高性能仿真器UVS+:https://www.univista-isg.com/site/product_detail/441

下一代全功能高效能数字验证调试平台UVD+:https://www.univista-isg.com/site/product_detail/442

碾压级动力提升:下一代全场景验证硬件系统UVHS-2发布!

合见工软发布下一代全场景验证硬件系统UniVista Unified Verification Hardware System Gen2(UVHS-2),最大可级联高达192片AMD Versal? Premium VP1902 Adaptive SoC,为大规模 ASIC/SoC 软硬件验证提供多样化应用场景设计,可广泛适用于 AI 智算、数据中心、HPC 超算、智能驾驶、5G 通信、智能手机、PC、IoT 等各类芯片的开发过程。作为高效的软硬件验证解决方案,UVHS-2能够大幅缩短芯片验证周期,加速芯片上市进程。

2023年合见工软发布了第一代全场景验证硬件系统 UVHS,经由市场打磨,已在多家客户的主流大芯片项目中部署,实现了多家客户全芯片级别的软硬件验证并协助客户成功流片迭代,客户包括中兴微电子、燧原科技、清华大学、达摩院玄铁、北京开源芯片研究院等。

相较于上一代产品 UVHS,UVHS-2在多个关键性能指标上实现了显著提升:容量提升超 2 倍,运行性能提升 1.5-2 倍,调试容量和带宽提升 4 倍。其基于 AMD Versal? Premium VP1902 Adaptive SoC,FPGA 核心性能最高可达 100MHz。在扩展规模方面,UVHS-2 系统最大级联规模可达 192 颗,逻辑门数量超过 150 亿门。借助合见工软核心技术——全局时序驱动的自动分割引擎,即便在超大规模系统场景下,仍能保持 10MHz 以上的 FPGA 跨片性能。UVHS-2也提供充足且可配置的互联通道,能够灵活支撑系统扩展需求。

合见工软首席技术官贺培鑫博士在发布会演讲中表示:“从2022年发布第一款时序驱动的原型验证平台,到如今性能可比肩国际标杆产品的下一代全场景硬件验证系统UVHS-2,合见工软的硬件验证产品线在三年来保持着持续高速的研发创新步伐,并得到了广泛的客户认可和商业部署。此次发布的UVHS-2平台从核心处理器升级、级联规模和双模架构创新提升等方面,为用户带来了更大容量、更高效率、更强性能三大核心优势。UVHS-2提供了更多新的验证范式跃迁,实现更灵活的软硬件协同仿真,显著加速验证周期,帮助客户提升流片成功率。现在,合见工软已实现从IP级到超大规模系统级验证的全线覆盖,全面支撑中国数字芯片设计与验证自主可控。”

客户评价:

芯原微电子GPU产品研发副总裁张慧明表示:“合见工软的UVHS平台是芯原Vivante GPU IP全流程交付流程中的重要验证平台。其超大容量FPGA原型验证能力帮助我们构建了从IP集成、系统验证到软件生态的一站式解决方案,为客户提供可快速落地的GPU参考设计套件。该平台不仅支持早期GPU系统级环境搭建,更实现了硬件与软件开发的全周期协同,在AI智算、智能汽车等领域大幅缩短了我们客户的项目周期。随着算力芯片复杂度提升,基于与合见工软的战略合作,芯原将与国内EDA企业共同探索,加速下一代Chiplet异构计算平台的规模化落地。”

更多产品信息,请访问:https://www.univista-isg.com/site/product_detail/443

推动智算互联:下一代核心协议IP支撑未来网络基建

合见工软今日发布超以太网IP解决方案UniVista UEC MAC IP,大幅提升网络性能和可靠性,推动智算互联从“通用连接”向“高性能计算网络”的进化,重塑AI基础设施格局,更好的为AI/ML、HPC(高性能计算)和云数据中心场景提供底层支撑。合见工软超以太网UEC MAC IP现已成功在高性能计算、人工智能AI、数据中心等复杂网络领域IC企业芯片中部署。

随着时代的发展,智算芯片在人工智能和高性能计算领域的应用取得了卓越的进展,但同时也对智算芯片的组网规模、带宽密度、多路径、对拥塞的快速反应以及数据流执行度的相互依赖等方面提出了更高的要求。

合见工软创新推出的超以太网 UEC MAC IP符合国际超以太网联盟(Ultra Ethernet Consortium,简称UEC)协议的物理层和链路层的IP标准,在传统以太网IP的基础上,扩展支持了UEC的物理层和链路层的功能,尤其是LLR(链路层重传)和CBFC(基于信用的流控)的功能,实现了网络的无损传输以及可靠性的提升。

同时,合见工软UEC MAC IP的推出,可与原有的智算网络IP解决方案UniVista RDMA IP和针对智算网络Scale-up应用的 ETH-X传输层协议解决方案UniVista PAXI IP相互协同,进一步扩大了合见工软在智算芯片互联IP技术领域的优势。

合见工软副总裁杨凯表示:“UEC是下一代数据中心和AI计算网络的核心协议,其重要性不仅体现在技术革新上,更对全球算力基础设施的竞争格局产生深远影响,特别是对中国产业来说,急需高性能的智算网络方案来推动智算集群的性能的提高。合见工软创新推出的超以太网 UEC MAC IP,实现了网络可靠性的大幅提升,推动传统以太网升级为超算级网络,支撑未来AGI时代我国的算力和网络基础设施建设。合见工软志在将真正自主可控的IP产品和EDA产品一起为客户提供完整可靠的芯片设计方案。”

合见工软的高速接口IP解决方案已实现了国产化技术突破,引领智算、HPC、通信、自动驾驶、工业物联网等领域大算力芯片的性能突破及爆发式发展。

更多产品信息,请访问:https://www.univista-isg.com/site/product_detail/444

高端芯片的自主可控:先进接口IP方案助力流片成功

合见工软今日发布国产自主研发支持多协议的32G SerDes PHY 解决方案UniVista 32G Multi-Protocol SerDes IP (简称UniVista 32G MPS IP)。该多协议PHY产品可支持PCIe5、USB4、以太网、SRIO、JESD204C等多种主流和专用协议,并支持多家先进工艺,成功应用于高性能计算、人工智能AI、数据中心等复杂网络领域IC企业芯片中部署。

UniVista 32G MPS IP由硬化模块(PMA/SerDes)和RTL模块(Raw PCS)组成,支持高达 32 Gbps 的数据传输速率(例如PCIe Gen5速率下32.0GT/s),全面支持 PCIe Gen1-5、USB4、以太网(25GKR、10GKR)、SRIO、JESD204C等多种主流和专用协议。其SerDes接口更提供多种数据位宽选项,具备独立的发送和接收同步时钟,并包含训练功能。UniVista MPS IP可充分满足数据中心、高性能计算、网络设备等应用领域对高速互连的严苛需求,经过严格验证与深度评估,可在各种应用场景中均表现出优异的稳定性和可靠性。

合见工软副总裁刘矛表示:“在数据量以指数级增长的时代,高性能计算、智算、数据中心等应用都对芯片底层互联与外部数据通信提出了更严苛的要求,高速串行通信SerDes作为互联接口的核心技术,对国产高端数字芯片的自主可控需求至关重要。合见工软UniVista 32G MPS IP解决方案,凭借高性能、高稳定性、低能耗和灵活配置,满足高速数据传输需求,为客户提供高可靠性的先进接口IP整体解决方案,经过实际验证,可帮助客户在面对新的接口实现应用时,大幅提高性能和改善能效,实现一次性流片成功,缩短产品的上市周期。合见工软志在将真正自主可控的IP产品和EDA产品一起为客户提供完整可靠的芯片设计方案。”

合见工软目前可提供的广泛IP解决方案包括:UniVista PCIe Gen5完整解决方案,以太网(Ethernet)、灵活以太网(FlexE)、Interlaken等多种高速互联接口控制器,ETH-X传输层协议(PAXI)IP和VIP产品,智算网络解决方案RDMA IP,Memory 接口HBM3/E、DDR5 、LPDDR5 IP,HiPi标准IP/VIP,针对先进封装芯粒(Chiplet)集成的关键标准UCIe IP,并实现国产首个跨工艺节点的UCIe IP互连技术验证,在采用台积电N6和三星SF5工艺制造的UCIe测试芯片之间成功完成互操作性测试,实现D2D和C2C互连应用。